想到週一早上還得去南港佈置Computex展場就沒力了...orz

想到週一早上還得去南港佈置Computex展場就沒力了...orz

"It's not about perfect. It's about effort. And when you implement that effort into your life… every single day, that's where transformation happens. That's how change occurs. Keep going, remember why you started."

星期六, 5月 31, 2008

The Inquirer還真是不遺餘力的唱衰nVidia GT200啊...

Nvidia GT200 sucessor tapes out

Nvidia GTX260 and 280 revealed

不過我倒是覺得GT200會是一個指標,證明fabless design house結合專業晶圓代工,能不能做出夠格且良率夠高的高階大晶片...如果可以,那這個產業未來的發展就很有意思了,即使機會不大。

Nvidia GTX260 and 280 revealed

不過我倒是覺得GT200會是一個指標,證明fabless design house結合專業晶圓代工,能不能做出夠格且良率夠高的高階大晶片...如果可以,那這個產業未來的發展就很有意思了,即使機會不大。

星期四, 5月 29, 2008

和預期的差不多

Dell reveals AMD Barcelona benchmarks

SPECint_rate2006

雙Barcelona 2.5GHz→92.4

雙Harpertown 3.2GHz→121

四Barcelona 2.5GHz→167

四Tigerton 2.93GHz→177

SPECfp_rate2006

雙Barcelona 2.5GHz→82.1

雙Harpertown 3.2GHz→80.4

四Barcelona 2.5GHz→152

四Tigerton 2.93GHz→108

反正情況和過去沒啥不同,AMD K8/K10在整體系統架構的優勢還是相當明顯,現在就只等著看QPI能不能讓Intel翻身了。

SPECint_rate2006

雙Barcelona 2.5GHz→92.4

雙Harpertown 3.2GHz→121

四Barcelona 2.5GHz→167

四Tigerton 2.93GHz→177

SPECfp_rate2006

雙Barcelona 2.5GHz→82.1

雙Harpertown 3.2GHz→80.4

四Barcelona 2.5GHz→152

四Tigerton 2.93GHz→108

反正情況和過去沒啥不同,AMD K8/K10在整體系統架構的優勢還是相當明顯,現在就只等著看QPI能不能讓Intel翻身了。

Labels:

Computer,

CPU,

HPC,

ProcessorWatch,

Server

星期三, 5月 28, 2008

星期一, 5月 26, 2008

星期日, 5月 25, 2008

「沒東西可出,勉強擴大既有結構」的過渡性產物

GeForce GTX 200 series

Radeon HD 4000 series

反正...我下一台桌機不太可能出現GT200和RV770吧...這兩個都讓人看了很沒力。

話說回來,我過去還用了不少nVidia的東西呀。以下是桌機顯示卡歷史表:

S3 Trio64V+ 2MB(啟亨)

Matrox Millennium 2MB

Matrox Mystique 2MB + Voodoo

nVidia RivaTNT 16MB(華碩)

nVidia GeForce 2MX(泡菜的Sumo)

nVidia GeForce Ti 4200(Abit)

nVidia GeForce 6600GT AGP(技嘉)

nVidia GeForce 7600GS AGP(青雲)→現役中

換句話說,除了Thinkpad X31外,近年來都是nVidia的天下。

下一張顯示卡會是哪張呢...天知道。

Radeon HD 4000 series

反正...我下一台桌機不太可能出現GT200和RV770吧...這兩個都讓人看了很沒力。

話說回來,我過去還用了不少nVidia的東西呀。以下是桌機顯示卡歷史表:

S3 Trio64V+ 2MB(啟亨)

Matrox Millennium 2MB

Matrox Mystique 2MB + Voodoo

nVidia RivaTNT 16MB(華碩)

nVidia GeForce 2MX(泡菜的Sumo)

nVidia GeForce Ti 4200(Abit)

nVidia GeForce 6600GT AGP(技嘉)

nVidia GeForce 7600GS AGP(青雲)→現役中

換句話說,除了Thinkpad X31外,近年來都是nVidia的天下。

下一張顯示卡會是哪張呢...天知道。

星期五, 5月 23, 2008

九年過去了,1999年的這段話依舊讓人津津樂道

Even though IBM disdains IA-64’s EPIC approach, it appears to be stealing a page from Intel’s playbook. In the same way that Intel usurped RISC principles to implement its x86 CISC architecture in P6, IBM plans to expropriate VLIW principles to implement its RISC architecture in Power4.

Even though IBM disdains IA-64’s EPIC approach, it appears to be stealing a page from Intel’s playbook. In the same way that Intel usurped RISC principles to implement its x86 CISC architecture in P6, IBM plans to expropriate VLIW principles to implement its RISC architecture in Power4.IBM only vaguely described the mechanism, but apparently in the early stages of the pipeline, the Power4 CPU groups instructions into VLIW-like bundles. These bundles are dispatched to issue queues, where individual instructions are held until their dependencies are resolved and then issued to the execution units. The pipeline beyond the issue stage is noninterlocked; so, once issued, nothing stops an instruction from completing, but all instructions in a bundle must complete before the bundle is retired.

Unlike conventional superscalar implementations that track individual instructions from dispatch through completion, the Power4 CPU tracks bundles only. According to IBM, this mechanism, along with data-flow sequencing through the noninterlocked pipelines, dramatically simplified the Power4 implementation, cutting the percentage of control logic in half compared with that of the four-issue Power3 design. This brought the control complexity of Power4 more in line with that of a VLIW machine while preserving the advantages of dynamic scheduling.

IBM said that the out-of-order-completion resources in the Power4 CPU are deep enough to hide the full latency of an L2 cache hit, which is probably 8–10 cycles. Also, to a greater extent than on any previous Power or PowerPC processor, Power4 will exploit the architecturally specified weak-storage-ordering model to reorder memory transactions and hide memory latency.

Each Power4 CPU implements the same ISA as IBM’s current RS/6000 and AS/400 systems and is also fully PowerPC compatible. IBM did, however, make some improvements that will be invisible to programs. The company is finally acknowledging that some of the complex instructions retained from the original 1990 POWER definition may not have been such great ideas. These instructions hinder the ability to run dynamically scheduled wide-issue processors at high frequency.

Convinced, however, that instruction-set stability is critical to its customer base, IBM didn’t take the radical step of expunging these instructions from the ISA. Instead, it has introduced instruction-set layering into Power4.

In this strategy, the hardware is optimized for the simple instructions, making no frequency compromises for complex ones. Slightly complex instructions, such as the base-registerupdate form of loads and stores, are cracked into two simple instructions by the instruction decoders. Moderately complex instructions, such as the string ops, are executed by a simple non-branching microcode engine. The most complex instructions, such as the old POWER instructions that were removed in PowerPC, trap to software emulation routines.

In this way, existing binaries run unmodified, but new binaries created by compilers aware of the layering may run faster by exploiting the faster alternatives.

星期四, 5月 22, 2008

星期一, 5月 19, 2008

シェリル!シェリル!シェリル!

資料來源: Animelo Summer Live 2008 -Challenge-

May'n [出演:8月31日(日)]

PROFILE

話題の新作アニメ『マクロスF』の歌姫、銀河の妖精“シェリル・ノーム”の歌を担当する『歌シェリル』ことMay’n。 18歳とは思えないステージングとONE&ONLYな伸びのあるハイトーンヴォイスでその名は瞬く間に知れ渡り、聴く人全てを魅了し続けている。 5月8日に"シェリル・ノーム starring May'n”名義で発売されたsingleはオリコン初登場3位を記録! 翌日の文化放送1F サテライトプラスLIVEではEVENT史上最高記録となる1000人を動員する等、今やおしもおされぬ“超銀河”人気アーティストである。

LINK

「私の歌を聴け~!!!」

「射手座☆午後九時Don't be late!」

幹,我好想去聽啊~(echo)

Labels:

ACG

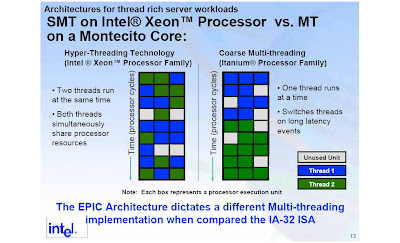

晚上來豪洨HyperThreading...

Update: 斯斯有兩種,HyperThreading有幾種?

Update: 斯斯有兩種,HyperThreading有幾種?

Labels:

Computer,

CPU,

Magazine,

PCADV,

ProcessorWatch

星期日, 5月 18, 2008

上週這個時候的亂拍:苗栗九華山(5/11)

上週日下午難得閒閒沒事幹,打電話給某長輩問說晚上要不要一起大食。啥?已經準備要出門下苗栗拍照了?二話不說,馬上跟上。

不過說真的,我還真羨慕Nikon D3的內建水平感測器呀,被大風吹得東倒西歪,唉唉。

星期六, 5月 17, 2008

最後還是找到自己的blog...

因為手邊沒有可動的Pentium 4系統,更罔論測試64 bits的Prescott,就抱著死馬當活馬醫的精神,拜求Google大神給我Pentium 4的ALU latency/throughput...

結果,竟然找到自己過去的文章,哇靠,原來這份文件一直都有在持續更新呀!甚至把Merom都包進去了。

倒是這兩篇論文,應該會是電腦王七月專欄內容的重心吧...加上Prescott的64 bits大解密,看來圖解會畫不完了...

Wave-Pipelining: A Tutorial and Research Survey

Wave Pipelining and Case Study (Pentium 4 and Itanium 2)

說到這個,今天中午才被人在墾丁的大長輩在電話裡面唸了一頓,說我給他錯誤的資訊害他在三年多前寫出錯誤的文章,哈哈哈~

揭露NetBurst微架構的真正面貌,七月,才開始。

結果,竟然找到自己過去的文章,哇靠,原來這份文件一直都有在持續更新呀!甚至把Merom都包進去了。

倒是這兩篇論文,應該會是電腦王七月專欄內容的重心吧...加上Prescott的64 bits大解密,看來圖解會畫不完了...

Wave-Pipelining: A Tutorial and Research Survey

Wave Pipelining and Case Study (Pentium 4 and Itanium 2)

說到這個,今天中午才被人在墾丁的大長輩在電話裡面唸了一頓,說我給他錯誤的資訊害他在三年多前寫出錯誤的文章,哈哈哈~

揭露NetBurst微架構的真正面貌,七月,才開始。

Labels:

Computer,

CPU,

Magazine,

ProcessorWatch

星期五, 5月 16, 2008

幹...真的還假的?我眼睛沒看錯吧?

日立アドバンストサーバ HA8000シリーズ

不管,下次一定要和Hitachi的PM喝的昏天暗地,哼哼。

「日経ソリューションビジネスが実施した姑且不論公正性,這看了真是令人百感交集啊...(淚目)

「第10回 パートナー満足度調査 PCサーバ部門」において、

HA8000シリーズが総合満足度1位を獲得しました。」

不管,下次一定要和Hitachi的PM喝的昏天暗地,哼哼。

星期四, 5月 15, 2008

星期三, 5月 14, 2008

看來Johan De Gelas也看不下去「從DIY看天下」的鄉民了

AMD's K10: a "dead" product or not?

"Yes, projecting the bad performance of the desktop chip to say that "AMD's products are a dead forest" is ... just silly."這句話講的實在太好了。

星期二, 5月 13, 2008

星期一, 5月 12, 2008

原來上週五樓下有一場如此精彩的嘴砲秀...

[First Look] ASUS EPU是天大謊言?-技嘉指控華碩EPU主機板造假!

無緣躬逢其盛。orz

說真的,姑且不論真偽,這則新聞有完全照登消息來源之嫌,沒有編輯自己的獨立判斷,這樣並不好。但話說回來啦,台灣今天有能力分析這種「高度技術問題」的編輯,又有幾人?能搞清楚PWM到底在幹嘛的大概都不太多了吧?

我期待所有媒體會怎麼處理這個議題。

無緣躬逢其盛。orz

說真的,姑且不論真偽,這則新聞有完全照登消息來源之嫌,沒有編輯自己的獨立判斷,這樣並不好。但話說回來啦,台灣今天有能力分析這種「高度技術問題」的編輯,又有幾人?能搞清楚PWM到底在幹嘛的大概都不太多了吧?

我期待所有媒體會怎麼處理這個議題。

星期六, 5月 10, 2008

我也好想知道哪裡有Intel的文件可抄襲呀!XD

剛剛在看癮科技對電腦王的評論時,意外看到的留言:

我也好想知道哪裡有這麼好的現成自婊文件可以抄襲呀!請這位擔任法務的小姐(?)告訴我吧!XD

「3.2008年5月號第46期:第186頁~第190頁我的感想是...

這個人的文章每次都是抄襲Intel的文件,自以為抄一抄人家原廠文件,把英文文件翻譯成中文沒人知道,就能說自己厲害,結果一看原來都是Intel 原廠文件東西,裡面的圖片就都漏餡了

(建議改善方法:所有的圖請美工或美術編輯重畫)」

我也好想知道哪裡有這麼好的現成自婊文件可以抄襲呀!請這位擔任法務的小姐(?)告訴我吧!XD

Labels:

bailan,

Computer,

CPU,

ProcessorWatch,

Roadmap

電腦王「達人之路」roadmap

老實講,真沒想到PC Shopper和PC Office都倒了,真不知道城邦某人到底在「自慢」什麼,唉,搞倒這麼多本雜誌難道會很自爽嗎?

反正,效法AMD新版roadmap「務實」的精神,先把去年連載計畫丟到一旁,重新制定未來的計畫。

目前碩果僅存的電腦王,達人之路已連載內容如下:

反正,效法AMD新版roadmap「務實」的精神,先把去年連載計畫丟到一旁,重新制定未來的計畫。

目前碩果僅存的電腦王,達人之路已連載內容如下:

- 2007八月:發掘x86處理器的隱憂

- 2007十月:Intel Pentium Pro的大冒險與P6微架構的奇蹟(上)

- 2008一月:Intel Pentium Pro的大冒險與P6微架構的奇蹟(中)

- 2008二月:Intel Pentium Pro的大冒險與P6微架構的奇蹟(下)

- 2008三月:簡介動態分支預測的基礎觀念

- 2008四月:NetBurst微架構的悲劇之第一部曲:Pentium 4問世的時代背景,與其技術核心Trace Cache

- 2008五月:NetBurst微架構的悲劇之第二部曲:回顧Trace Cache概念在Intel處理器的發展及應用

- 2008六月:NetBurst微架構的悲劇之第三部曲:為何Prescott效能不佳?(已交稿)

- 2008七月:NetBurst微架構的悲劇之第四部曲:Prescott微架構的秘密與其過熱的主因(動筆

腸穿孔中) - 2008八月:NetBurst微架構的悲劇之第五部曲:從一點都不high的Hyper-Threading:探討SMT在x86的應用及限制(資料整理中,這題目其實蠻好寫的,牽扯到IBM Power5的奇蹟和對Nehalem的預期)

- 2008九月:Concluding Remarks:過去一年的回顧篇(休養生息兼資料補充

外加騙稿費用,不過這得看電腦王編輯部同不同意,哈)

- 從無用的cmov指令檢視x86上的Predicated/Guarded Execution

- 回顧x86 SIMD extensions發展史

- 為何x86難以進入高階server?限制何在?

- Transmeta Crusoe/CMS的悲劇

- AMD K7/K8的奇蹟

- 撞上熱量之牆的x86

- 他山之石可以攻錯:Intel IA-64的大反動

Labels:

Computer,

CPU,

PCADV,

ProcessorWatch,

Roadmap

星期四, 5月 08, 2008

結果AMD還是自己先公佈roadmap了

如此一來,上次的胡言亂語,一切謎底都揭曉了。

一、延長既有Socket F和K10的壽命,解放HyperTransport「暗藏」的潛力:

嗯嗯,嗚嗚,啊啊,怎麼跑出了「Socket F1」呀?

二、降低系統平臺的整體製造成本,如主機板上的晶片數目:

BYE BYE,Socket G3和G3MX。

三、減少「實際上」開發的CPU晶片數量,沒必要為了新腳位和小幅度更動cache容量就開新晶片:

Istanbul和Sao Paolo,實際上應該是同一顆晶片,只是腳位不同。

事實上,Shanghai/Suzuka已經把DDR3 controller和4 port ccHT3做上去了,6 core的Istanbul沒理由不這樣作,如此一來,AMD就可以縮短戰線,持續最佳化Istanbul的layout以提高時脈,並且集中力量開發全新Bulldozer微架構的Sandtiger。

不過,這樣看來,K8微架構在市場上存活十年,真是驚人...

隱而不現的是...這樣看來,nVidia和Broadcom ServerWorks的晶片組,還會在AMD Opteron平臺存活好一段時日,哈。nVidia狀況連連的晶片組部門可以稍微喘口氣了。

Labels:

Computer,

CPU,

ProcessorWatch,

Roadmap,

Server

星期一, 5月 05, 2008

這才是真正的豪洨

濕婆-Wikipedia

印度史詩《羅摩衍那》中有一段「恆河的起源」,這故事說,印度教大神濕婆和烏瑪交媾,一次就達100年之久,中間從不間斷,眾神對濕婆的生殖能力感到驚慌,就央求濕婆把他的精液傾瀉到恆河之中,這就是恆河之水從天而來的原因。

Labels:

bailan

星期四, 5月 01, 2008

[限制級洨言洨語]誤交損友,一生不覺

過去數年,我認識的不少涼濕液莠良師益友,其高風亮節都僅限於嘴砲層面上的,例如「小心我給妳一點顏射顏色瞧瞧」、「看我對妳洨以大液曉以大義」、「可惡!妳竟然不肯陪我打砲!自己出門!難道要我自己一個人手淫守營嗎?哼,但出門請別忘了帶淫具營具啊!XD」、「幫我把那個肛鋼塞放回去呀!」、「他是我肛交剛交到的網友」、「燃燒吧!我的洨小宇宙!」等等。

事隔多年,達爾文的「進化論」在這些人身上,都得到了具體的解釋,像:

一、「水球,我每天上床前都是畜處男,而我的夜夜都是第一次。XD」

二、「水球,我每晚都會失身,但起床後就是畜處男了。XD」

三、「水球,我每早起床都是畜處男,但...過十分鐘馬上就失身了。XD」

結論:本痴漢果然出淤泥而不染啊...(把酒臨空)

事隔多年,達爾文的「進化論」在這些人身上,都得到了具體的解釋,像:

一、「水球,我每天上床前都是

二、「水球,我每晚都會失身,但起床後就是

三、「水球,我每早起床都是

結論:本痴漢果然出淤泥而不染啊...(把酒臨空)

訂閱:

意見 (Atom)